# EVALAg9900 Rev 1 Evaluation Board User Manual

Rev 1.0 - September 2016

| 1 | Tak | ole | of | Co | nter | nts |

|---|-----|-----|----|----|------|-----|

|---|-----|-----|----|----|------|-----|

| 1 | Ta                                  | ble of Contents                              | 1 |  |  |  |

|---|-------------------------------------|----------------------------------------------|---|--|--|--|

| 2 | Ta                                  | ble of Figures                               | 1 |  |  |  |

| 3 | 3 Introduction                      |                                              |   |  |  |  |

| 4 | Вс                                  | pard Description                             | 2 |  |  |  |

|   | 4.1                                 | Input Selection and Classification           | 2 |  |  |  |

|   |                                     | Class Programming                            |   |  |  |  |

|   |                                     | Power Output                                 |   |  |  |  |

|   |                                     | Output adjustment                            |   |  |  |  |

| _ | 4.5                                 | 1                                            | 4 |  |  |  |

| 5 | Typical Set-up                      |                                              |   |  |  |  |

| 6 |                                     |                                              |   |  |  |  |

|   |                                     | Typical Application                          |   |  |  |  |

|   |                                     | EVALAG9900 Rev 1- Evaluation Board Schematic |   |  |  |  |

|   | 6.3                                 | Link settings                                | 7 |  |  |  |

|   |                                     |                                              |   |  |  |  |

|   |                                     |                                              |   |  |  |  |

|   |                                     |                                              |   |  |  |  |

|   |                                     |                                              |   |  |  |  |

| 2 | Ta                                  | able of Figures                              |   |  |  |  |

| _ | _                                   |                                              | _ |  |  |  |

|   | Figure 1: Board Layout              |                                              |   |  |  |  |

|   | Figure 2: Output Ripple Measurement |                                              |   |  |  |  |

|   | igure 3: Basic set-up               |                                              |   |  |  |  |

| Г | igure 4: Example set-up6            |                                              |   |  |  |  |

#### 3 Introduction

This manual is intended to be a guide to using the "EVALAg9900 Rev 1" evaluation board with an Ag9912M Powered Device (PD) module.

The EVALAg9900 evaluation board can be powered using the spare pair in the CAT5e cable (pins 4 & 5 and pins 7 & 8), or over the data pair through on-board magnetics.

The EVALAG9900 evaluation board has been designed to handle 10GBASE-T Ethernet data rates.

## 4 Board Description

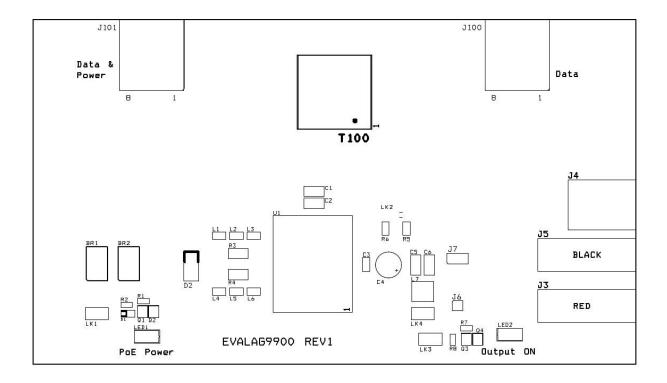

The input data and power is supplied to the board through connector J101. The data is passed through to the peripheral equipment via J100, with the output power from the Ag9900 module supplied via J3 to J5 (see Figure 1 & 4).

The EVALAg9900 on-board bridge rectifiers will ensure that the correct input polarity is applied to the Ag9900M.

LED 1 indicates that power is being supplied to the Ag9900M. This can be disabled by removing the jumper link LK1, removing this link does not affect the power being delivered to the Ag9900M.

## 4.1 Input Selection and Classification

The PSE output is automatically extracted from either the spare pairs or from the center taps of T100.

BR1 and BR2 are fitted to ensure that the PSE output polarity is correctly delivered to the VIN+ and VIN- (input) pins of the Ag9900M module.

The EVALAG9900 evaluation board has ferrite beads fitted on each input to reduce emissions, see apps notes "ANX-POE-EMI" and ANX-POE-HDBaseT" on our website for more information

Figure 1: Board Layout

# 4.2 Class Programming

The Ag9900M is internally set to Class 0, so the EVALAG9900 evaluation board does not have any class programming.

# 4.3 Power Output

The Ag9900M output is delivered from connectors J3 (positive) and J5 (negative). In addition to these the output voltage is also available from J4 (the center pin is positive).

LED2 is illuminated when the Ag9900M output is ON and LK3 is fitted.

# 4.4 Output adjustment

The output voltage of the Ag9900M can be adjusted by connecting the ADJ pin to either the -VDC or the +VDC pins. LK2 can be used to adjust the output voltage (see Figure 1).

On the EVALAG9900 evaluation board R5 and R6 are fitted with a 0 Ohm link to give its full adjustment, see the output adjustment section in the datasheet for more information.

With LK2 fitted above R5 (center to right) the output voltage will be decreased.

With LK2 fitted above R6 (center to left) the output voltage will be increased.

#### 4.5 Output Filter

The EVALAG9900 evaluation board has an output PI filter fitted, to reduce the output ripple. The PI filter is disabled when the link LK4 is fitted, but can be activated by simply removing the link LK4 (see Figure 1).

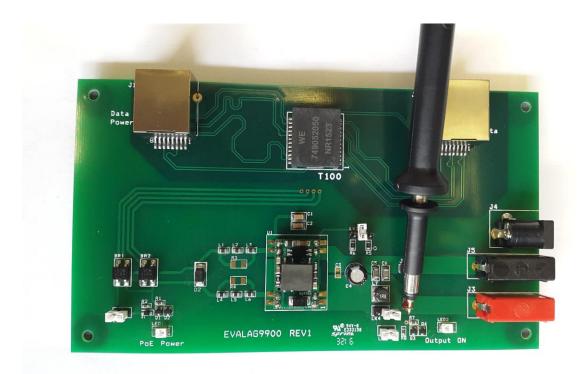

To measure the output ripple correctly positions J7 and J6 have been fitted for a scope tip to be placed inside J6 with the barrel resting on J7. (See Figure 2 below).

Figure 2: Output Ripple Measurement

# 5 Typical Set-up

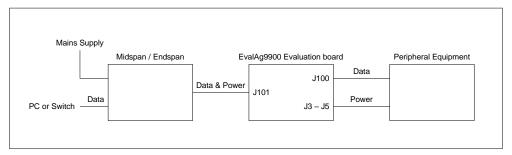

Figure 3 shows the basic set up using the POE evaluation board with a High Power Midspan or Endspan.

The equipment required: -

- > Midspan or Endspan PSE (Power Sourcing Equipment)

- > Peripheral (or Test) Equipment

- > CAT5e cables

- > Output power cable

- Mains cable

Figure 3: Basic set-up

# 6 Using the Board

#### 6.1 Typical Application

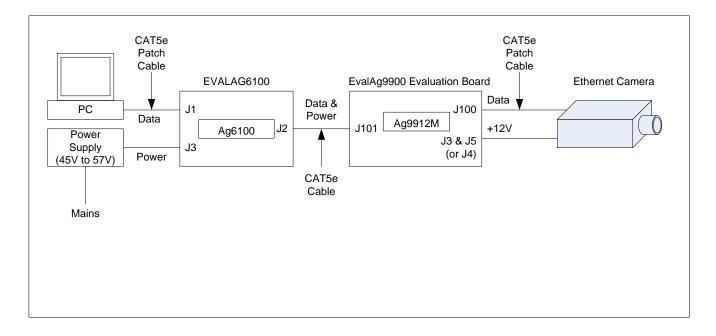

Figure 4 shows the full test set-up using an EVALAG9900 board and an EVALAG6100 board supplying +12V to an Ethernet camera.

The PC ethernet port is connected to the data input of the EVALAG6100 board (J1) via a short Cat5e patch cable. The Data & Power output from the EVALAG6100 board (J2) is connected to the input of the EVALAG9900 board (J101) via a CAT5e cable. The data output of the EVALAG9900 board (J100) is connected to the data port of the ethernet camera via a CAT5e cable. The (+12V) power output from the EVALAG9900 board is connected to the dc input of the ethernet camera.

Figure 4: Example set-up

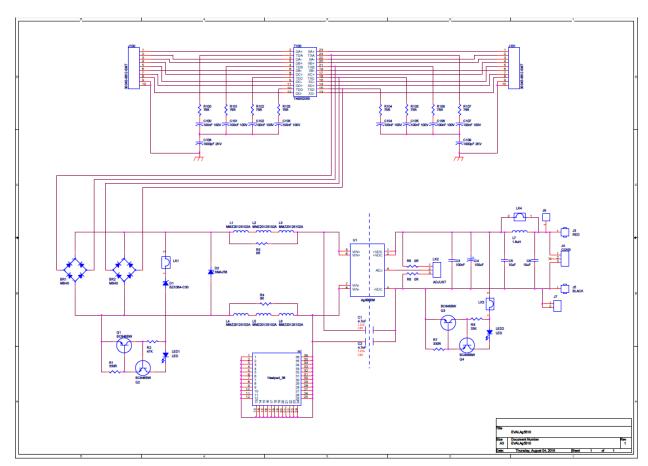

#### 6.2 EVALAG9900 Rev 1- Evaluation Board Schematic

# 6.3 Link settings

LK1 – Input LED

LK2 – Output adjust select

LK3 – Output LED

LK4 - Output Filter

J6 & J7 – Output Filter Measure